重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

更多“硬件电路设计,主要是根据功能要求来设计。()”相关的问题

更多“硬件电路设计,主要是根据功能要求来设计。()”相关的问题

第1题

A、硬件电路设计时,原理图是根据功能要求来设计的

B、硬件电路设计时,不要设计出PCB

C、硬件电路设计时,要对器件选型,并提供物料清单(BOM)表

D、硬件电路设计时,原理图出来后最好进行仿真论证

第2题

数控分频器的设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计数控分频器电路,建立数控分频器的实验模式。通过电路仿真和硬件验证,进一步了解数控分频器的功能和特性。

设计原理

数控分频器的元件符号如图所示,CLK是时钟输入端,D[7..0]是数据输入端,FOUT是数控频率输出端,COUT是进位(溢出)输出端。数控分频器的输出频率受到数据D[7..0]的控制,当D[7..0]数据值越大,输出频率越高。

第3题

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计边沿JK触发器电路,建立边沿JK触发器的实验模式。通过电路仿真和硬件验证,进一步了解边沿JK触发器的功能和特性。

设计原理

边沿JK触发器的元件符号如图所示,CLK是时钟输入端,下降沿有效;J1、J2和J3是3个具有与关系的J输入端,K1、K2和K3是3个具有与关系的K输入端;PRN是异步置1(置位)输入端,低电平有效,CLRN是异步置0(复位)输入端,低电平有效;Q是触发器的输出端,QN是反相输出端。

第4题

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计基本RS触发器电路,建立基本RS触发器的实验模式。通过电路仿真和硬件验证,进一步了解基本RS触发器的功能和特性。

设计原理

基本RS触发器可以由两个与非门或者两个或非门构成。由两个与非门构成的基本RS触发器的原理图如图所示,其中RDN是异步置0输入端,低电平有效;SDN是异步置1输入端,低电平有效;Q是触发器的输出端,QN是反相输出端。由图所示的电路可知,基本RS触发器的输出表达式为

(2.2.1)

第5题

全加器设计

为了便于读者完成HDL及可编程逻辑器件实验,本实验以全加器设计为基础,介绍Altera公司的Quartus II(7.0版本)软件的使用方法,包括设计输入、编译、仿真、引脚锁定、编程下载和硬件验证等操作。目前,能够完成设计电路硬件验证的设备种类繁多,不同的设备有各自的功能特点和使用方法,不过它们都具有建立(或选择)实验模式、确定引脚锁定方案和编程下载等方面的操作。下面仅以伟福EDA6000系列SOPC/DSP/EDA通用实验开发系统(以下简称为EDA6000)为例,介绍设计电路的硬件验证的操作方法。

实验要求

用原理图输入设计法和Verilog HDL文本输入设计法设计全加器电路,建立全加器的实验模式。通过电路仿真和硬件验证,进一步了解全加器的功能。

设计原理

考虑自低位来的进位的加法运算称为“全加”,能实现全加运算的电路称为全加器。1位全加器的真值表如表所示,表中的A、B是两个1位二进制加数的输入端;CI是低位来的进位输入端;SO是和数输出端;CO是向高位的进位输出端。根据真值表写出电路输出与输入之间的逻辑关系表达式为

,

。

| 全加器真值表 | |

| A B CI | SO CO |

| 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 | 0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 1 |

第6题

需要有8个数字量输入,用于采集设备的状态信息;且需要8个数字量输出,用于控制设备动作。

具备一个RS-232接口,可以和上位机连接,接收上位机发送的命令及参数。

需要提供一个基准定时信号,定时时间间隔为0.01秒。

需要彩色LCD显示器,用于显示状态信息等。

根据上述功能要求的描述,若采用S3C2410芯片为核心来构建该机械设备控制器的硬件平台,请完善下面的叙述和C语言程序(需要使用的控制寄存器的格式见题后说明)。

(1)若硬件设计时采用GPIO端口E的GPE0~GPE7引脚作为8个数字量输出,那么软件设计时其初始化语句是:rGPECON=(rGPECON|0x00005555)&___【1】____。若软件设计时需要通过GPE5引脚输出“1”来驱动执行机构动作,那么语句是:rGPEDAT= rGPEDAT | ___【2】____。(注:rGPECON是端口E的控制寄存器所对应的变量,rGPEDAT是端口E的数据寄存器所对应的变量)

(2)硬件设计时,选用UART0来完成RS-232接口电路设计。在软件设计时,其初始化程序中波特率设置为9600bps,数据格式设置为:8位数据位、奇校验、1位停止位。请补充完善下面的UART0初始化函数(注:主频参数为PCLK):

voidUART0_Init()

{

rGPHCON=(rGPHCON&0xFFFFFF00)|___【3】____; //端口H相应引脚功能初始化

rUFCON0=0x0; //FIFO不使能

rUMCON0=0x0;

rULCON0=___【4】____; //设置线路控制寄存器

rUCON0=0x145; //设置控制寄存器

rUBRDIV0=((int)(PCLK/___【5】____) 1); //设置波特率,小数采用四舍五入

}

(3)按照上面UART0初始化函数所设置的通信速率,每秒钟最多能传输___【6】____个字节的信息。若上位机有大小为4KB的初始参数需要下载到控制器中,那么,约需传输____【7】___秒才能完成下载(1K=1024,精确到小数点后面1位数字)。

(4)系统中所需要的0.01秒基准定时时间选用S3C2410芯片内部的Timer0部件来产生。若系统的主频参数PCLK为264MHz,分频器值选择为16,预分频系数选择为3,那么,Timer0的计数常数为___【8】____。软件设计时,设计了如下的Timer0初始化函数,请补充完善。(注:下面程序中⑨、⑩、⑿用8位十六进制数表示,⑾用4位十六进制数表示)

voidTimer0Int(void)

{

//设置定时器配置寄存器0(TCFG0)

rTCFG0=___【9】____; //Timer0预分频系数选择为3,该寄存器中其它无关位均为0

//设置定时器配置寄存器1(TCFG1)

rTCFG1=___【10】___; // Timer0分频器值为16,该寄存器中其它无关位均为0

//设置计数常数

rTCNTB0=___【11】____; //设置控制寄存器TCON

rTCON=___【12】____;//更新TCNTB0和TCMPB0,该寄存器中其它无关位均为0

rTCON=0x00000009;//设置Timer0自动装载,并启动

}

(5)彩色LCD显示屏的硬件接口电路由S3C2410的专用GPIO端口__【13】_____和端口___【14】____相关引脚配以驱动电路来设计。软件设计时,需要通过设置它们控制寄存器的值分别为___【15】____和____【16】___来确定它们的引脚功能。

(6)系统的软件可以设计为在无操作系统的环境下运行。设计者自行设计系统的启动引导程序,在该程序中完成异常向量设置、堆栈指针设置以及必要的硬件初始化。ARM9体系结构中规定的IRQ异常所对应的异常向量地址为___【17】____。Timer0部件所产生的0.01秒基准时间到时将引起IRQ异常。由于IRQ异常向量地址与下一个异常向量地址之间间隔为___【18】____个字节,因此,通常在IRQ异常向量地址处设计一条转移指令。堆栈指针的设置需按工作模式来进行。设置IRQ模式下的堆栈指针,需在R0“清0”后用指令ORRR1,R0,0x12|___【19】____和MSRCPSR_CXSF,R1来使CPU核进入IRQ模式,然后再给SP寄存器赋值作为该模式下的堆栈指针。这些初始化工作完成后,即可通过指令___【20】____来引导应用程序的主函数main()。

说明:下面是试题解答时需要用到的寄存器格式及相关说明。

1)端口C的控制寄存器(GPCCON)

引脚GPCCON的位描述

GPC15[31:30]00=输入,01=输出,10=VD7,11=保留

GPC14[29:28]00=输入,01=输出,10= VD6,11=保留

GPC13[27:26]00=输入,01=输出,10= VD5,11=保留

GPC12[25:24]00=输入,01=输出,10= VD4,11=保留

GPC11[23:22]00=输入,01=输出,10= VD3,11=保留

GPC10[21:20]00=输入,01=输出,10= VD2,11=保留

GPC9[19:18]00=输入,01=输出,10= VD1,11=保留

GPC8[17:16]00=输入,01=输出,10= VD0,11=保留

GPC7[15:14]00=输入,01=输出,10=LCDVF2,11=保留

GPC6[13:12]00=输入,01=输出,10= LCDVF1,11=保留

GPC5[11:10]00=输入,01=输出,10=LCDVF0,11=保留

GPC4[9:8]00=输入,01=输出,10=VM,11=IIS数据输出

GPC3[7:6]00=输入,01=输出,10=VFRAME,11= IIS数据输入

GPC2[5:4]00=输入,01=输出,10=VLINE,11=保留

GPC1[3:2]00=输入,01=输出,10=VCLK,11=保留

GPC0[1:0]00=输入,01=输出,10=LEND,11=保留

2)端口D的控制寄存器(GPDCON)

引脚GPDCON的位描述

GPD15[31:30]00=输入,01=输出,10=VD23,11=保留

GPD14[29:28]00=输入,01=输出,10= VD22,11=保留

GPD13[27:26]00=输入,01=输出,10= VD21,11=保留

GPD12[25:24]00=输入,01=输出,10= VD20,11=保留

GPD11[23:22]00=输入,01=输出,10= VD19,11=保留

GPD10[21:20]00=输入,01=输出,10= VD18,11=保留

GPD9[19:18]00=输入,01=输出,10= VD17,11=保留

GPD8[17:16]00=输入,01=输出,10= VD16,11=保留

GPD7[15:14]00=输入,01=输出,10= VD15,11=保留

GPD6[13:12]00=输入,01=输出,10= VD14,11=保留

GPD5[11:10]00=输入,01=输出,10= VD13,11=保留

GPD4[9:8]00=输入,01=输出,10= VD12,11=保留

GPD3[7:6]00=输入,01=输出,10= VD11,11=保留

GPD2[5:4]00=输入,01=输出,10= VD10,11=保留

GPD1[3:2]00=输入,01=输出,10= VD9,11=保留

GPD0[1:0]00=输入,01=输出,10= VD8,11=保留

3)端口E的控制寄存器(GPECON)

引脚GPECON的位描述

GPE15[31:30]00=输入,01=输出,10=IICSDA,11=保留

GPE14[29:28]00=输入,01=输出,10=IICSCL,11=保留

GPE13[27:26]00=输入,01=输出,10=SPICLK0,11=保留

GPE12[25:24]00=输入,01=输出,10=SPIMOSI0,11=保留

GPE11[23:22]00=输入,01=输出,10=SPIMISO0,11=保留

GPE10[21:20]00=输入,01=输出,10=SSDAT3,11=保留

GPE9[19:18]00=输入,01=输出,10=SSDAT2,11=保留

GPE8[17:16]00=输入,01=输出,10=SSDAT1,11=保留

GPE7[15:14]00=输入,01=输出,10=SSDAT0,11=保留

GPE6[13:12]00=输入,01=输出,10=SDCMD,11=保留

GPE5[11:10]00=输入,01=输出,10=SDLCK,11=保留

GPE4[9:8]00=输入,01=输出,10=IISSDO,11=IIS数据输出

GPE3[7:6]00=输入,01=输出,10=IISSI,11= IIS数据输入

GPE2[5:4]00=输入,01=输出,10=CDCLK,11=保留

GPE1[3:2]00=输入,01=输出,10=IISCLK,11=保留

GPE0[1:0]00=输入,01=输出,10=IISLRCK,11=保留

4)端口H的控制寄存器(GPHCON)

引脚GPHCON的位描述

GPH10[21:20]00=输入,01=输出,10=CLKOUT1,11=保留

GPH9[19:18]00=输入,01=输出,10= CLKOUT0,11=保留

GPH8[17:16]00=输入,01=输出,10=UEXTCLK,11=保留

GPH7[15:14]00=输入,01=输出,10=RXD2,11=保留

GPH6[13:12]00=输入,01=输出,10=TXD2,11=保留

GPH5[11:10]00=输入,01=输出,10=RXD1,11=保留

GPH4[9:8]00=输入,01=输出,10=TXD1,11=IIS数据输出

GPH3[7:6]00=输入,01=输出,10=RXD0,11= IIS数据输入

GPH2[5:4]00=输入,01=输出,10=TXD0,11=保留

GPH1[3:2]00=输入,01=输出,10=nRTS0,11=保留

GPH0[1:0]00=输入,01=输出,10=nCTS0,11=保留

5)UART线路控制寄存器(ULCONn n可以是0、1、2)

ULCONn的位[7][6][5:3][2][1]描述保留

值为0确定红外模式

0=正常操作模式

1=正常操作模式确定校验类型

0xx=无校验

100=奇校验

101=偶校验确定停止位数

0=1位停止位

1=2位停止位确定数据位

00=5位01=6位

10=7位11=8位6)TCFG0寄存器

TCFG0的位功能描述初始状态值

[31:24]保留0x00[23:16]在此不用0x00

[15:8]确定Timer2,Timer3,Timer4的预分频系数0x00[7:0]确定

Timer0,Timer1的预分频系数0x007)TCFG1寄存器

TCFG1的位功能描述初始状态值[31:24]保留0x00

[23:20]在此不用0b0000

[19:16]确定Timer4的分频器值0000=2 0001=4 0010=8 0011=16

[15:12]确定Timer3的分频器值0000=2 0001=4 0010=8 0011=16

[11:8]确定Timer2的分频器值0000=2 0001=4 0010=8 0011=16

[7:4]确定Timer1的分频器值0000=2 0001=4 0010=8 0011=16

[3:0]确定Timer0的分频器值0000=2 0001=4 0010=8 0011=16

说明:设置TCFG0、TCFG1可以确定预分频器系数、分频器值,如:通过设置TCFG0为0x0000001F,Timer0的预分频器系数选择为31,设置TCFG1为0x00000001,Timer0的分频器值选择为4。通过下面公式计算定时器的计数常数:

定时器输入时钟频率=PCLK/(预分频系数+1)/分频器值

计数常数=定时时间间隔/(1/定时器输入时钟频率)

预分频系数的范围为0~255,分频器值的取值范围为2、4、8、16。

6)TCON寄存器(注:此处不用的位被省略,其值默认为0x0000000)

TCON的位功能描述初始状态值厖0x0000000[3]确定Timer0的自动装载功能

1=自动装载0=一次停止0b0[2]确定Timer0的输出反转位

1=TOUT0反转0=TOUT0不反转0b0[1]确定Timer0的更新

1=更新TCNTB0和TCMPB0 0=不更新0b0[0]确定Timer0的启动/停止

1=启动0=停止0b0

第7题

a、需要一个视频摄像模块,用于采集汽车行驶中周围环境的视频图像,图像分辨率为320?40。

b、需要“回放”、“下载”、“删除”3个命令按键。

c、需要一个320?40的彩色LCD显示屏。

d、采集视频图像的同时,需要记录当前的实时时间,精确到秒。

f、需要一个通信接口,在视频图像下载时用来传输视频图像。

根据上述功能要求的描述,若采用S3C2410芯片为核心来构建该行车记录仪的硬件平台,请完善下面的叙述(程序)和回答有关的问题。

(1)若硬件设计时采用GPIO端口E的GPE15、GPE14引脚连接基于I2C总线的视频摄像模块的___【1】____信号引脚和__【2】___信号引脚。那么,驱动程序中需要用语句:rGPECON=(rGPECON|0xA0000000)&___【3】____来初始化GPE15、GPE14引脚为I2C总线功能的引脚。(注:rGPECON是端口E的控制寄存器,其格式如图1所示)

(2)若摄像模块所采集的一帧视频图像,其分辨率为320?40,原始图像的颜色数据格式为Y:U:V=8:4:4,那么,一帧图像的原始图像信息需要的存储容量为___【4】____KB(1K=1024)。若视频信号每秒需要16帧图像,那么,一段1分钟的视频,其原始图像信息约需___【5】____MB的存储空间。在设计下载通信接口电路时,考虑到即使采用115200bps的速率,下载一段1分钟的视频至少需要用时约___【6】____小时(精确到小数点后1位),因此,采用异步串行口(即RS-232接口)来下载就不合适。

(3)设计彩色LCD显示屏的接口电路时,可以采用S3C2410芯片中专用于连接LCD显示屏的____【7】___端口和____【8】___端口来设计。3个命令按键:“回放”、“下载”、“删除”,分别连接到GPE0、GPE1、GPE2。若按键按下时,对应的GPIO引脚将为“0”,否则为“1”。那么,在相关驱动程序中,可以用语句:rGPECON= rGPECON &___【9】____来初始化GPE0、GPE1、GPE2为输入,而不影响GPE端口的其它引脚功能,并用下面一段语句来判断是哪个命令按键被唯一按下。

temp= rGPEDAT & 0x0007; //temp是一个8位二进制变量,rGPEDAT是端口E的数据寄存器

switch(temp)

{case ___【10】____ ://判断是否“回放”按键被唯一按下

厖//省略了其他语句

case ___【11】____ ://判断是否“下载”按键被唯一按下

厖//省略了其他语句

case ___【12】____ ://判断是否“删除”按键被唯一按下

厖//省略了其他语句

}

(4)采集视频图像的同时,所需记录的实时时间,通过读取S3C2410芯片内部的RTC部件来获得。该部件进行读写时,需要先置位___【13】____,然后再进行读写。读写操作完成后,需要___【14】____该位。在相关驱动程序中,可以用下面一段语句来初始化该部件。

voidRTC_init(void)

{

//初始化相关寄存器

rRTCCON= (rRTCCON|___【15】____);// rRTCCON是控制寄存器变量,其格式如图2所示。

rRTCALM=___【16】____;//报警功能(即闹钟)全部禁止

rRTCRST= 0x00;

rTICNT= ___【17】____; //时间间隔设置为1s

rRTCCON= (rRTCCON&___【18】____);

厖//省略了其他语句

}

RTCCON的位名称RTCCON的位号描述

CLKRST3RTC时钟计数复位,0=不位,1=复位

CNTSEL2BCD码计数器选择:0=组合BCD码,1=分离BCD码

CLKSEL1BCD码计数时钟选择:0=晶体频率/215,1=保留

RTCEN0RTC读/写使能:0=禁止,1=允许

图2 rRTCCON的格式

(5)用于下载视频图像的通信接口采用USB接口较合适,并且,图像信息需要压缩。因此,移植一个Linux操作系统作为软件平台,使其能在本行车记录仪硬件上运行,将便于其应用软件的开发。软件平台的构建步骤通常是:首先移植___【19】____程序;然后再完成Linux内核的移植,内核移植完成后还需构建___【20】____文件系统。

说明:下面是试题解答时需要用到的寄存器格式及相关说明。

1)端口C的控制寄存器(GPCCON)

引脚GPCCON的位描述

GPC15[31:30]00=输入,01=输出,10=VD7,11=保留

GPC14[29:28]00=输入,01=输出,10= VD6,11=保留

GPC13[27:26]00=输入,01=输出,10= VD5,11=保留

GPC12[25:24]00=输入,01=输出,10= VD4,11=保留

GPC11[23:22]00=输入,01=输出,10= VD3,11=保留

GPC10[21:20]00=输入,01=输出,10= VD2,11=保留

GPC9[19:18]00=输入,01=输出,10= VD1,11=保留

GPC8[17:16]00=输入,01=输出,10= VD0,11=保留

GPC7[15:14]00=输入,01=输出,10=LCDVF2,11=保留

GPC6[13:12]00=输入,01=输出,10= LCDVF1,11=保留

GPC5[11:10]00=输入,01=输出,10=LCDVF0,11=保留

GPC4[9:8]00=输入,01=输出,10=VM,11=IIS数据输出

GPC3[7:6]00=输入,01=输出,10=VFRAME,11= IIS数据输入

GPC2[5:4]00=输入,01=输出,10=VLINE,11=保留

GPC1[3:2]00=输入,01=输出,10=VCLK,11=保留

GPC0[1:0]00=输入,01=输出,10=LEND,11=保留

2)端口D的控制寄存器(GPDCON)

引脚GPDCON的位描述

GPD15[31:30]00=输入,01=输出,10=VD23,11=保留

GPD14[29:28]00=输入,01=输出,10= VD22,11=保留

GPD13[27:26]00=输入,01=输出,10= VD21,11=保留

GPD12[25:24]00=输入,01=输出,10= VD20,11=保留

GPD11[23:22]00=输入,01=输出,10= VD19,11=保留

GPD10[21:20]00=输入,01=输出,10= VD18,11=保留

GPD9[19:18]00=输入,01=输出,10= VD17,11=保留

GPD8[17:16]00=输入,01=输出,10= VD16,11=保留

GPD7[15:14]00=输入,01=输出,10= VD15,11=保留

GPD6[13:12]00=输入,01=输出,10= VD14,11=保留

GPD5[11:10]00=输入,01=输出,10= VD13,11=保留

GPD4[9:8]00=输入,01=输出,10= VD12,11=保留

GPD3[7:6]00=输入,01=输出,10= VD11,11=保留

GPD2[5:4]00=输入,01=输出,10= VD10,11=保留

GPD1[3:2]00=输入,01=输出,10= VD9,11=保留

GPD0[1:0]00=输入,01=输出,10= VD8,11=保留

3)端口E的控制寄存器(GPECON)

引脚GPECON的位描述

GPE15[31:30]00=输入,01=输出,10=IICSDA,11=保留

GPE14[29:28]00=输入,01=输出,10=IICSCL,11=保留

GPE13[27:26]00=输入,01=输出,10=SPICLK0,11=保留

GPE12[25:24]00=输入,01=输出,10=SPIMOSI0,11=保留

GPE11[23:22]00=输入,01=输出,10=SPIMISO0,11=保留

GPE10[21:20]00=输入,01=输出,10=SSDAT3,11=保留

GPE9[19:18]00=输入,01=输出,10=SSDAT2,11=保留

GPE8[17:16]00=输入,01=输出,10=SSDAT1,11=保留

GPE7[15:14]00=输入,01=输出,10=SSDAT0,11=保留

GPE6[13:12]00=输入,01=输出,10=SDCMD,11=保留

GPE5[11:10]00=输入,01=输出,10=SDLCK,11=保留

GPE4[9:8]00=输入,01=输出,10=IISSDO,11=IIS数据输出

GPE3[7:6]00=输入,01=输出,10=IISSI,11= IIS数据输入

GPE2[5:4]00=输入,01=输出,10=CDCLK,11=保留

GPE1[3:2]00=输入,01=输出,10=IISCLK,11=保留

GPE0[1:0]00=输入,01=输出,10=IISLRCK,11=保留

4)端口H的控制寄存器(GPHCON)

引脚GPHCON的位描述

GPH10[21:20]00=输入,01=输出,10=CLKOUT1,11=保留

GPH9[19:18]00=输入,01=输出,10= CLKOUT0,11=保留

GPH8[17:16]00=输入,01=输出,10=UEXTCLK,11=保留

GPH7[15:14]00=输入,01=输出,10=RXD2,11=保留

GPH6[13:12]00=输入,01=输出,10=TXD2,11=保留

GPH5[11:10]00=输入,01=输出,10=RXD1,11=保留

GPH4[9:8]00=输入,01=输出,10=TXD1,11=IIS数据输出

GPH3[7:6]00=输入,01=输出,10=RXD0,11= IIS数据输入

GPH2[5:4]00=输入,01=输出,10=TXD0,11=保留

GPH1[3:2]00=输入,01=输出,10=nRTS0,11=保留

GPH0[1:0]00=输入,01=输出,10=nCTS0,11=保留

5)UART线路控制寄存器(ULCONn n可以是0、1、2)

ULCONn的位[7][6][5:3][2][1]描述保留

值为0确定红外模式

0=正常操作模式

1=正常操作模式确定校验类型

0xx=无校验

100=奇校验

101=偶校验确定停止位数

0=1位停止位

1=2位停止位确定数据位

00=5位01=6位

10=7位11=8位6)TCFG0寄存器

TCFG0的位功能描述初始状态值

[31:24]保留0x00[23:16]在此不用0x00

[15:8]确定Timer2,Timer3,Timer4的预分频系数0x00[7:0]确定

Timer0,Timer1的预分频系数0x007)TCFG1寄存器

TCFG1的位功能描述初始状态值[31:24]保留0x00

[23:20]在此不用0b0000

[19:16]确定Timer4的分频器值0000=2 0001=4 0010=8 0011=16

[15:12]确定Timer3的分频器值0000=2 0001=4 0010=8 0011=16

[11:8]确定Timer2的分频器值0000=2 0001=4 0010=8 0011=16

[7:4]确定Timer1的分频器值0000=2 0001=4 0010=8 0011=16

[3:0]确定Timer0的分频器值0000=2 0001=4 0010=8 0011=16

说明:设置TCFG0、TCFG1可以确定预分频器系数、分频器值,如:通过设置TCFG0为0x0000001F,Timer0的预分频器系数选择为31,设置TCFG1为0x00000001,Timer0的分频器值选择为4。通过下面公式计算定时器的计数常数:

定时器输入时钟频率=PCLK/(预分频系数+1)/分频器值

计数常数=定时时间间隔/(1/定时器输入时钟频率)

预分频系数的范围为0~255,分频器值的取值范围为2、4、8、16。

6)TCON寄存器(注:此处不用的位被省略,其值默认为0x0000000)

TCON的位功能描述初始状态值厖0x0000000[3]确定Timer0的自动装载功能

1=自动装载0=一次停止0b0[2]确定Timer0的输出反转位

1=TOUT0反转0=TOUT0不反转0b0[1]确定Timer0的更新

1=更新TCNTB0和TCMPB0 0=不更新0b0[0]确定Timer0的启动/停止

1=启动0=停止0b0

第8题

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计四总线缓冲器(CT74125)电路,建立四总线缓冲器的实验模式。通过电路仿真和硬件验证,进一步了解四总线缓冲器的功能和特性。

设计原理

四总线缓冲器CT74125的元件符号如图所示,输入端为A(A4~A1),输出端为Y(Y4~Y1),ENN是使能控制输入端,低电平有效,当ENN=0时,输出Y=A;当ENN=1时Y=Z(高阻态)。

第9题

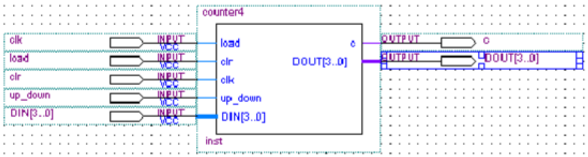

4位二进制加法计数器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4位二进制加法计数器电路,建立4位二进制加法计数器的实验模式。通过电路仿真和硬件验证,进一步了解4位二进制加法计数器的功能和特性。

设计原理

4位二进制加法计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;CLRN是复位输入端,低电平有效;Q[3..0]是计数器的状态输出端;COUT是进位输出端。

第10题

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计有时钟使能的2位十进制计数器电路,建立有时钟使能的2位十进制计数器的实验模式。通过电路仿真和硬件验证,进一步了解有时钟使能的2位十进制计数器的功能和特性。

设计原理

有时钟使能的2位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENB是时钟使能控制输入端,高电平有效,当ENB=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效;Q[3..0]是计数器低4位状态输出端,Q[7..3]是高4位状态输出端;COUT是进位输出端。

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!