重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.3

B.6

C.8

D.16

更多“一个数据选择器的地址端有3个时,最多可以有 个数据输入信号。”相关的问题

更多“一个数据选择器的地址端有3个时,最多可以有 个数据输入信号。”相关的问题

第3题

A、使用数据选择器可实现时序逻辑电路

B、二进制译码器相当于是一个最小项发生器,便于实现组合逻辑电路

C、多谐振荡器可产生矩形脉冲

D、一个数据选择器的地址输入端有3个时,最多可以有8个数据信号输出。??

第4题

第5题

A.另一地址译码器 B.输出缓冲器 C.负载数字部件 D.数据总线

第7题

阅读下列说明和图,回答问题1至问题3,将解答填入答题纸的对应栏内。

【说明】

在某嵌入式系统设计中,使用8片RAM进行64KRAM的外部存储器扩展,如图2-1所示。该CPU共有16根地址线,8根数据线,在设计中,利用CPU的 作为访问控制信号,该访问控制信号低电平有效。另外,

作为访问控制信号,该访问控制信号低电平有效。另外, 作为读写命令信号(高电平为读,低电平为写)。8片8Kx8位的RAM芯片与CPU相连,RAM芯片的片选内部为上拉电阻到电源,各个RAM芯片的片选信号和74138译码器的输出相连,译码器的地址选择端连接到CPU的A13,A14,A15地址线上。

作为读写命令信号(高电平为读,低电平为写)。8片8Kx8位的RAM芯片与CPU相连,RAM芯片的片选内部为上拉电阻到电源,各个RAM芯片的片选信号和74138译码器的输出相连,译码器的地址选择端连接到CPU的A13,A14,A15地址线上。

【问题1】(8分)

根据上图所示,写出RAM0,RAM1和RAM7的地址范围(请用16进制进行表示)。

RAM0: (1)

RAM1: (2)

RAM7: (3)

若CPU操作的地址总线为A800H,结合图2-1所示的示意图,CPU访问的是哪个RAM存储器(4)。

【问题2】(4分)

如果运行时发现不论往哪片RAM写入数据后,以C000H为起始地址的存储芯片都有与其相同的数据,假设芯片与译码器可靠工作,则说明:

(1) RAM0~RAM7中(1) 的片选输入端总是处于低电平。

(2)如果有问题的存储芯片的片选输入端总是处于低电平,以下可能原因中描述不正确的是(2) 。

A.该存储芯片的CS端与存储芯片的 端错连或短路

端错连或短路

B.该存储芯片的CS端与CPU的 端错连或短路

端错连或短路

C.该存储芯片的CS端与地线错连或短路

D.该存储芯片的CS端悬空

【问题3】(3分)

根据连接图,若出现地址线A15与CPU断线,并搭接到高电平上,下面描述中正确的是( )。(该题为多选题)

A.此时存储器只能寻址A15=1的地址空间

B.此时存储器只能寻址总共64K字节空间的高32K字节地址空间

C.此时访问64K字节空间的高32K字节地址空间时会错误地访问到低32K字节地址空间

D.此时访问64K字节空间的低32K字节地址空间时会错误地访问到高32K字节地址空间

第8题

1. 在CCS中利用C语言编写C54x DSP程序时,需要运行时支持库支持,请简答以下问题。 (1)请简述运行时支持库的作用。 (3分) (2)如果选择使用rts.lib,请问在编译链接选项中选择使用“近调用”还是“远调用”? (2分) 2. 以TMS320C54x DSP为例,请分析DSP的中断处理系统: (1)写出确定TMS320VC54x DSP中断向量入口地址的计算方法?(2分) (2)如果IPTR设置为1FFH,计算INT0(中断号为16)的中断向量入口地址。(3分) 3. 写出TMS320C54x的数据寻址方式,注意至少要写出5种。 (5分) 4. (1)为什么要使用Bootloader程序?(3分) (2)在TMS320VC5416芯片的Bootloader 程序中,可以采用哪些方式进行Bootloader自举。(5分) (3) Bootloader程序使用的自举列表有哪两种方式? (2分) 5. 简述DSP芯片的特点。(5分) 6. 以TI TMS320VC5416 DSP作为主处理芯片,设计一个嵌入式系统通过其XF管脚输出频率为8KHz的方波信号。(10分) (1) 当外部输入时钟CLKIN为16MHz时,要求DSP以160MHz全速运行,在DSP程序初始化时应设置时钟模式寄存器CLKMD的值为多少,使TMS320VC5416全速运行?(4分) (2) 如果使用DSP的时钟中断进行方波输出设计(每发生一次中断改变一下XF输出的电平),请问其TDDR、PRD寄存器的值应设为多少?(DSP以160MHz全速运行)(6分) 7. 在基于C语言编程的TMS320VC5416 DSP嵌入式系统应用程序开发过程中,DSP的存储空间映射和分配是重要知识点,请分析解答以下存储空间映射和分配的问题。在DSP程序初始化时执行 #define PMST (volatile unsigned int*)0x1D *PMST = 0x7FA0 ; 语句后,请解释说明并绘制出数据存储空间、第0页程序存储空间的存储器映射图。(10分)

第9题

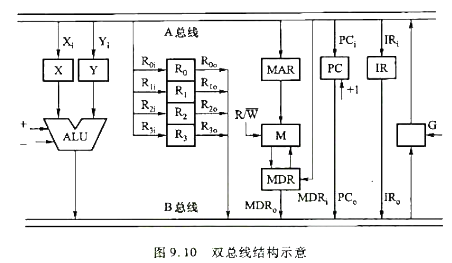

ADDR2,R0指令完成(R2)+(R0)→R,的操作,画出其指令周期信息流程图(假设指令的地址已放在PC中),并列出相应的微操作控制信号序列。

第10题

(1)“ADD R2,R0”指令完成(R0)+(R2)→R0的功能操作,画出其指令周期流程图,假设该指令的地址已放入PC中。并列出相应的微操作控制信号序列。

(2)若将“取指周期”缩短为一个CPU周期,请先画出修改数据通路,后画出指令周期流程图。

(3)在(2)的基础上,将“执行周期”也缩短为一个CPU周期,先修改运算器数据通路,后画出指令周期流程图。此时加法指令速度比(1)提高几倍?

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!