重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知操作符包括‘+’、‘-’、‘*’、‘/’、‘(’和‘)’。将中缀表达式 a+b-a*((c d)/e-f)+g 转换为等价的后缀表达式 ab+acd+e/f-*-g+时,用栈来存放暂时还不能确定运算次序的操作符,若栈初始时为空,则转换过程中同时保存在栈中的操作符的最 大个数是

A.5

B.7

C.8

D.11

更多“已知操作符包括‘+’、‘-’、‘*’、‘/’、‘(’和‘)’。将中缀表达式 a+b-a*((c d)/e-f)+g 转换为等价的后缀表”相关的问题

更多“已知操作符包括‘+’、‘-’、‘*’、‘/’、‘(’和‘)’。将中缀表达式 a+b-a*((c d)/e-f)+g 转换为等价的后缀表”相关的问题

第2题

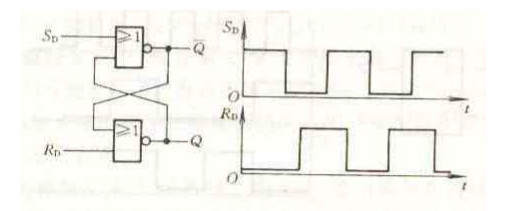

将下图所示的输入波形加在由两个或非门组成的基本RS触发器上,试画出输出Q和 端的波形(设初始状态为Q=0) 。

端的波形(设初始状态为Q=0) 。

第4题

基本RS触发器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计基本RS触发器电路,建立基本RS触发器的实验模式。通过电路仿真和硬件验证,进一步了解基本RS触发器的功能和特性。

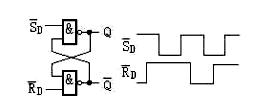

设计原理

基本RS触发器可以由两个与非门或者两个或非门构成。由两个与非门构成的基本RS触发器的原理图如图所示,其中RDN是异步置0输入端,低电平有效;SDN是异步置1输入端,低电平有效;Q是触发器的输出端,QN是反相输出端。由图所示的电路可知,基本RS触发器的输出表达式为

(2.2.1)

第6题

画出由或非门构成的基本RS触发器输出端Q和的电压波形,输入端SD和RD的电压波形分别如图题4.2所示。

第8题

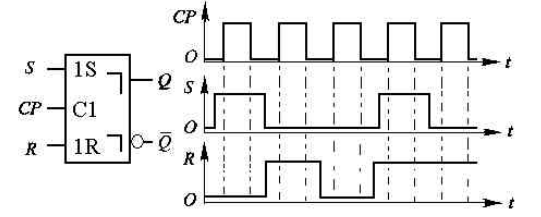

画出图5-12由或非门组成的基本RS锁存器输出端Q的电压波形,输入端R、S端的电压波形如图所示。

第9题

在图所示的由或非门组成的基本RS触发器中,加入图示的S和R波形,画出触发器Q和 输出端的波形。假设触发器的初始状态为0。

输出端的波形。假设触发器的初始状态为0。

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!